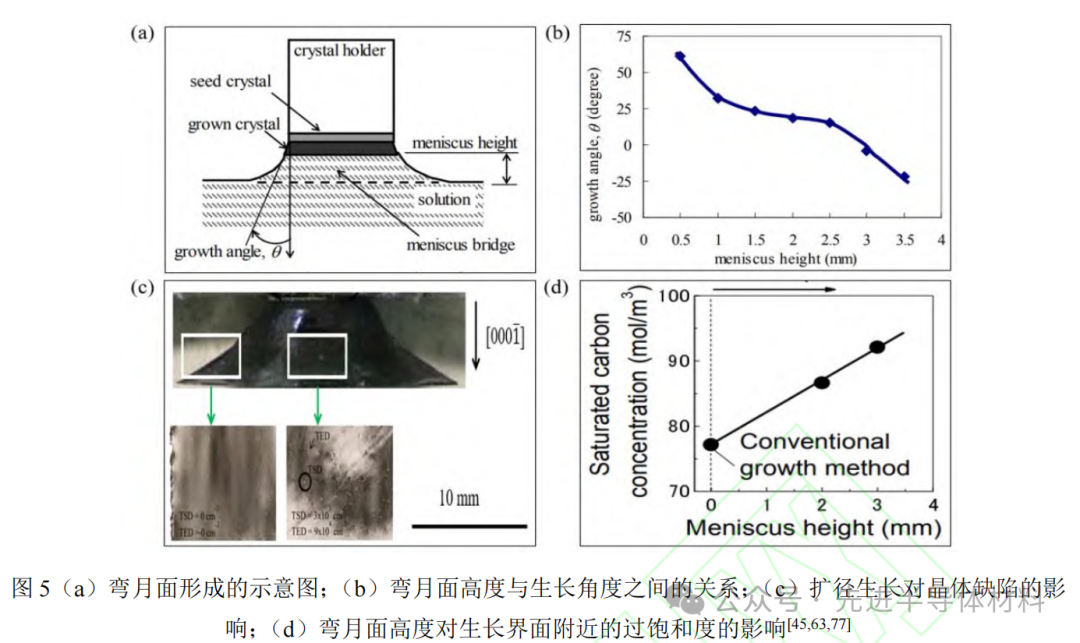

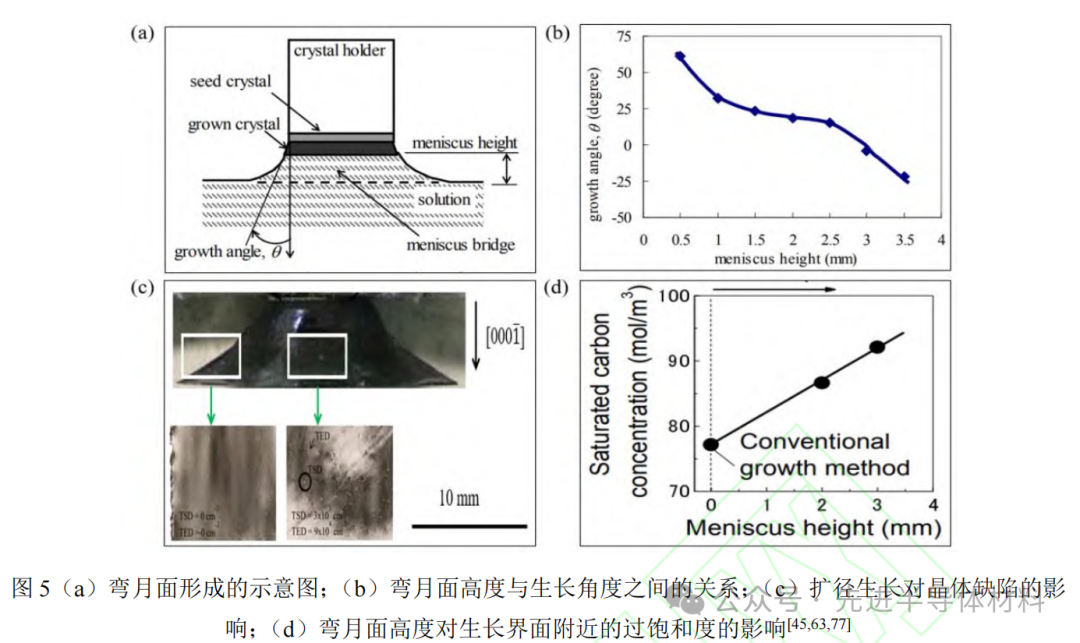

与PVT法不同的是,TSSG法生长SiC晶体过程中固-液界面附近具有更低的生长温度和更小的温度梯度,有助于弱化晶体内部应力并提高临界剪切应力值。同时,溶液法长晶过程中所释放的结晶潜热比气相法中释放的结晶潜热更低,可增强界面附近生长环境的稳定性。上述特点促使TSSG法在制备SiC晶体中表现出多方面的技术优势。微管是限制SiC材料应用的主要障碍之一,被称为“杀手型”缺陷,其存在会增加器件漏电流并降低击穿电压,甚至导致器件永久失效[57]。在PVT制备SiC晶体过程中,除了继承籽晶固有的缺陷外,不成熟的籽晶粘接技术和意外生成的夹杂包裹同样容易造成晶体内部新增微管并在后续晶体生长过程中被继承和延伸[58-59]。研究证实,利用TSSG法可以对衬底中已有的微管进行有效覆盖和闭合并确保在之后的生长过程中不会新增,从而实现真正意义上的零微管。利用PVT法制备的SiC晶体典型的贯穿型螺旋位错(TSD)、贯穿型刃型位错(TED)和基平面位错(BPD)密度分别为300~500、2000~5000及500~1000cm-2[10]。晶体内部过高的位错密度对于器件制造显然不利,尤其是BPD,将导致双极性器件严重退化。在今后的SiC电力电子领域中,进一步开发低位错化技术仍然是一个重要的课题。2004年Nakamura等利用PVT法并结合重复a面技术(RAF)成功制备了超高质量的SiC晶体,20mm直径的衬底的腐蚀坑密度(EPD)比传统PVT法制备的SiC衬底的EPD值低了三个数量级。2014年,Kondo等[62]利用RAF技术制备了6英寸高质量SiC衬底,其TSD和BPD分别为302cm-2和324cm-2。可见,RAF技术是降低位错密度、改善结晶质量极其有效的生长方法,但由于需要反复进行{112̅0面和{11̅00面的生长,对晶体尺寸要求很高,无论从技术还是成本上都存在很大的挑战。TSSG法制备SiC晶体过程中由于生长界面的温度分布较为均匀,释放的结晶潜热较低,所引起的热应力较小,进而可以有效抑制位错缺陷的增殖[63]。同时,该生长技术在位错转换和消除方面优势显著,晶体生长过程中表面宏观台阶会迫使沿晶体生长方向延伸的TSD和TED分别转变为基平面上的扩展型堆垛层错(SFs)和BPD缺陷,并进一步沿台阶流[112̅0]方向迁移,直至终止于晶体外侧,从而实现具有低位错密度的SiC晶体制备[64-66]。Yamamoto等[67]利用TSSG法在Si-Cr体系下制备了SiC晶体,指出相对于SiC籽晶,生长层内的TSD密度从2000cm-2减少至30cm-2,而BPD密度从2000cm-2减少至500cm-2,降幅显著。随着生长层厚度的增加,TSD密度将进一步降低,当厚度达到4.4μm时,TSD转换为扩展型缺陷的转换率达90%,进一步当生长层厚度为10μm时,转换率超过99%。为了将转换后的扩展型缺陷推移至晶体外侧,获得更高厚度的SiC晶体是十分必要的且所需生长的厚度与籽晶偏轴角度和晶体直径有关[66,68]。此外,位错的转换行为及转化效果与台阶高度、台阶形貌及台阶横向扩展速率存在强关联性,所谓台阶形貌是指基面与台阶斜面之间的夹角,夹角越大意味着台阶越陡峭。研究证实具有高且陡峭的生长台阶有助于增强位错转换效率,削弱位错沿垂直于生长面方向继承和传输的能力[69-70]。为了提高生长台阶高度,增强位错转换效果,一系列调控手段被相继提出,包括不限于:选用具有高偏轴角度的籽晶Si面作为生长面、在Si助溶剂中加入Ti或Cr元素或是在Si0.6Cr0.4体系的基础上添加Fe、V、Ni、Ti、Nb和Mn元素,尤其是Nb和Mn、调控溶液流速和流向及提高生长界面过饱和度等。但过度发育的宏观台阶容易诱导沟槽缺陷的产生并夹杂严重的溶剂包裹,甚至造成大量位错的新增。Matani等指出当宏观台阶高度在6~8μm时,TSD缺陷的转换率超过80%,然而当台阶高度在3~5μm时,夹杂有溶剂包裹的沟槽缺陷出现的概率大幅增加。因此,需严格调控台阶高度以平衡位错转换效率与宏观缺陷产生。此外,采用两步法和杂化法对于降低位错密度、提升晶体品质也是有效的措施[46,76]。Murayama等基于TSSG技术并利用两步法制备了具有极低位错密度的4H-SiC晶体,其中TSD、TED和BPD分别为11cm-2,385cm-2和28cm-2。然而,由于TSD作为螺旋台阶源,极低的TSD密度将难以维持晶型稳定并可能诱导其他缺陷的产生。Murayama等通过对籽晶结构进行重新设计并优化了热场分布,实现了具有低位错密度的单一4H-SiC晶型制备。增大SiC晶体直径可以显著地降低单个器件的制造成本。相比于6英寸,8英寸晶体可多切近90%数量的芯片且边缘浪费可降低7%,器件成本预计可降低20%~35%。众所周知,利用PVT法进行SiC晶体扩径生长是极其困难的,需要精准调控生长界面附近的热场和流场分布,否则容易导致晶体外围出现多晶生长或开裂并诱发各种缺陷,且迭代周期长,以年为单位。TSSG法在大尺寸晶体制备方面有着先天优势,可利用放肩技术实现晶体扩径生长。日本丰田公司Daikoku等利用弯月面控制技术并通过调节弯月面高度来改变生长角度,进而实现晶体直径的可控生长且扩径区域的结晶质量很高,几乎无位错缺陷,如图5(a)~(c)所示。弯月面高度将直接影响生长界面附近热量的耗散程度,随着高度的增加,位于生长界面附近的结晶潜热通过辐射方式被快速消除,进而造成该区域的过饱和度提高并加快晶体生长,如图5(d)所示。在实际的晶体生长过程中,受溶液挥发、坩埚刻蚀及提拉速率与结晶速率失配等影响,弯月面高度难以维持在一个相对平稳的区间,容易诱导多晶生长。为克服液面下降引起的弯月面高度增加的问题,可在长晶过程中有针对性地下移籽晶托或上移坩埚,以尽可能维持弯月面高度恒定,增强生长界面的稳定性。 通常,铝(Al)掺杂通过占据硅(Si)格位实现p型SiC衬底制备,而氮(N)掺杂通过占据碳(C)格位实现n型SiC衬底制备[75,78-79]。为了获得低电阻率的n型4H-SiC单晶衬底,增强N原子进入晶格并占据C格位的能力是十分关键的。在竞位效应的作用下,降低溶液中的碳浓度有助于增强N掺杂效果,且相比于Si面,籽晶C面更有助于实现高浓度掺杂[78]。Komatsu等[72]指出在Si0.6Cr0.4体系中加入Ti可以提高N掺杂效果,这是因为Ti对N具有很高的亲和力,增强了溶液对N的溶解度。目前利用溶液法制备SiC晶体可实现的最高掺杂浓度为1.1×1020cm-3,对应的电阻率达0.003Ω﹒cm,已优于传统PVT法所制备的n型SiC晶体的电学性能,达到了N在4H-SiC晶体中的固溶度极限。但为了避免高掺杂引起的堆垛层错和3C-SiC多型增殖,晶体内的N掺杂浓度需严格控制在3×1019cm-3以内,且对应的最低电阻率为0.01Ω·cm[78]。为克服过高氮掺杂浓度引起的各种缺陷,可适当地引入Al元素加以修饰[80-81]。Komatsu等[25]采用Si0.57Cr0.4Al0.01Sn0.02体系,在生长氛围N2/(He/H2)为0.9vol%时所生长的n型4H-SiC晶体的电阻率为12mΩcm,与市销的低电阻率n型4H-SiC晶片(~20mΩcm)相当甚至更低。

通常,铝(Al)掺杂通过占据硅(Si)格位实现p型SiC衬底制备,而氮(N)掺杂通过占据碳(C)格位实现n型SiC衬底制备[75,78-79]。为了获得低电阻率的n型4H-SiC单晶衬底,增强N原子进入晶格并占据C格位的能力是十分关键的。在竞位效应的作用下,降低溶液中的碳浓度有助于增强N掺杂效果,且相比于Si面,籽晶C面更有助于实现高浓度掺杂[78]。Komatsu等[72]指出在Si0.6Cr0.4体系中加入Ti可以提高N掺杂效果,这是因为Ti对N具有很高的亲和力,增强了溶液对N的溶解度。目前利用溶液法制备SiC晶体可实现的最高掺杂浓度为1.1×1020cm-3,对应的电阻率达0.003Ω﹒cm,已优于传统PVT法所制备的n型SiC晶体的电学性能,达到了N在4H-SiC晶体中的固溶度极限。但为了避免高掺杂引起的堆垛层错和3C-SiC多型增殖,晶体内的N掺杂浓度需严格控制在3×1019cm-3以内,且对应的最低电阻率为0.01Ω·cm[78]。为克服过高氮掺杂浓度引起的各种缺陷,可适当地引入Al元素加以修饰[80-81]。Komatsu等[25]采用Si0.57Cr0.4Al0.01Sn0.02体系,在生长氛围N2/(He/H2)为0.9vol%时所生长的n型4H-SiC晶体的电阻率为12mΩcm,与市销的低电阻率n型4H-SiC晶片(~20mΩcm)相当甚至更低。SiC功率器件在用作n沟道而不是p沟道时往往表现出更好的性能,但该类器件需要在低电阻率、高品质的p型衬底上外延生长,而目前商用的p型4H-SiC衬底具有相对较高的电阻率(约2.5Ω﹒cm)且质量有待进一步提升[13]。通常,利用PVT法制备p型SiC衬底时需加入Al4C3来提供Al源并通过调控Al蒸汽分压来改变掺杂浓度。但由于Al源在高温环境下具有高的饱和蒸汽压特性,导致晶体中的Al掺杂浓度极不均匀,难以获得持续稳定的p型掺杂并容易诱导多型夹杂缺陷的产生[82]。考虑到溶液法生长SiC晶体所需要的温度和温度梯度较小,有助于抑制Al组分的过度挥发,进而有效地提高晶体内部掺杂均一性。2014年,Shirai等基于Si-Cr-Al体系,利用溶液法成功生长了低电阻率(35mΩ﹒cm)的p型4H-SiC晶体且对应的Al掺杂浓度为10%(原子数分数),比目前商用的p型SiC衬底的电阻率低了两个数量级。

国内领先的快速退火炉RTP半导体设备厂商,拥有先进的控温技术,数十项专利证书,快速退火炉,RTA,RTP,合金炉,RTO,快速退火炉RTP,国产快速退火炉,自主研发,快速退火工艺,半导体设备,芯片退火设备,碳化硅退火,氮化镓退火,离子注入退火,晶圆快速退火,硅片快速退火,ast2800,mattson,allwin21,AG退火炉,jetfirst,unitemp,IC,集成电路,SIC,化合物,4寸,6寸,8寸,12寸,第三代半导体,屹唐,北方华创